Страница

10

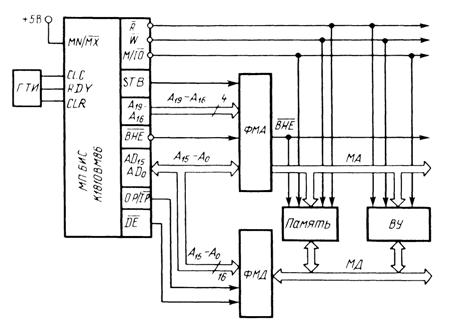

Рис. 4.1. Упрощенная схема МП БИС КР1810 ВМ86

Блок сопряжения с магистралями производит все пересылки данных и кодов для EU. Пересылки между МП БИС и памятью или внешними устройства-ми осуществляются по требованию EU. В то время как EU занят выполнением команды, блок BIU получает последующие в программе коды команд из памяти и сохраняет их в конвейере команд. В конвейере может быть записано до шести кодов команд. Это позволяет BIU выдавать в EU сохраненные команды по мере необходимости без загрузки внешних магистралей МП БИС. Блок BIU организует получение нового кода команды, как только два байта в конвейере команд будут переданы в EU. За один цикл получения кода команды в блок BIU записываются с МД два байта команды.

В большинстве случаев в BIU находится хотя бы одна команда и EU не ждет, пока очередная команда будет извлечена из памяти.

Коды команд подаются в EU последовательно так, как они записаны в программе. Если EU выполняет команду передачи управления в другое место программы, то BIU очищает конвейер команд, получает код команды из нового адреса, передает его в EU и начинает заполнять конвейер заново. Если EU требует обращения к памяти или внешнему устройству, то BIU приостанавливает процесс получения команд в конвейер и организует необходимый цикл обмена данными.

На рис. 4.2 приведен пример построения однопроцессорной системы.

Рис. 4.2. Структура микроЭВМ на базе МП БИС КР1810ВМ86

![]() Основная задача, решаемая в многопроцессорных системах, заключается в обеспечении распределения времени доступа каждого из процессоров к общей системной магистрали. Магистрали микроЭВМ представляют собой систему MULTIBUS, в состав которой входят 16-разрядная МД, 20-разрядная МА, восемь входов прерываний, шины управления и шины арбитража. Последние позволяют осуществить синхронизацию процесса использования системных магистралей при параллельной работе нескольких процессоров в системе. Для формирования шин управления и арбитража в таких системах применяются специальная схема системного контроллера и схема арбитража работы процессоров. Схемы используют следующие выводы МП БИС: RQ/EQ, RQ/E1, позволяющие сопроцессорам брать управление магистралями системы; QS0 и QS1, отображающие состояние конвейера команд и позволяющие внешним устройством или сопроцессорам системы следить за выполнением команд МП БИС; LOCK – сигнал, используемый для запрета доступа к магистралям на время выполнения текущей команды.

Основная задача, решаемая в многопроцессорных системах, заключается в обеспечении распределения времени доступа каждого из процессоров к общей системной магистрали. Магистрали микроЭВМ представляют собой систему MULTIBUS, в состав которой входят 16-разрядная МД, 20-разрядная МА, восемь входов прерываний, шины управления и шины арбитража. Последние позволяют осуществить синхронизацию процесса использования системных магистралей при параллельной работе нескольких процессоров в системе. Для формирования шин управления и арбитража в таких системах применяются специальная схема системного контроллера и схема арбитража работы процессоров. Схемы используют следующие выводы МП БИС: RQ/EQ, RQ/E1, позволяющие сопроцессорам брать управление магистралями системы; QS0 и QS1, отображающие состояние конвейера команд и позволяющие внешним устройством или сопроцессорам системы следить за выполнением команд МП БИС; LOCK – сигнал, используемый для запрета доступа к магистралям на время выполнения текущей команды.

4.2. Особенности проектирования МПC на основе однокристальных микроЭВМ и контроллеров.

Так же, как и при выполнении системного этапа проектирования любых ЭВМ, при проектировании МПC на основе однокристальных микроЭВМ с самого начала должны быть определены и документированы основные функциональные характеристики разрабатываемой системы: разработчики и изготовители МПС могут интерпретировать характеристики не так, как заказчик и это может привести к необходимости переделки уже выполненной работы.

Результатом этого этапа должна быть структурная схема МПС с определением всех входных и выходных сигналов и их электрических и временных характеристик. На этом же этапе желательно составить так называемый "служебный обзор", в котором форма задания функциональных характеристик заказчика заменяется на более удобную для разработчика. Толкование этого документа должно иметь полное понимание и однозначность. Можно также внести предложения по улучшению характеристик и параметров МПС, которые заинтересуют заказчика. Выбор MП MПC - достаточно сложная процедура, при которой надо учитывать множество факторов. Если, например, доступна только одна модель однокристального МП, то проблема выбора сводится к ответу на вопрос: можно ли построить МПС с требуемыми характеристиками на основе этого МП. При разработке МПС с предполагаемым большим объемом выпуска выбор и проверка правильности принятого решения требуют значительного времени.

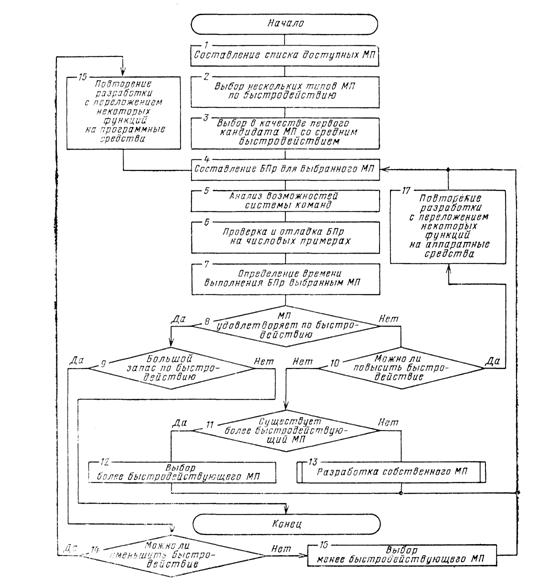

Так как одним из главных критериев при выборе MП является требуемое быстродействие, наиболее распространенным методом его оценки является использование так называемых б е н ч м а р к о в с к и х программ (БПр). БПр - это программа решения на анализируемом МП такой задачи, которая по составу операций соответствует классу задач предполагаемого применения. Обычно длина БПр – 100-200 команд. В состав ее обязательно должны входить операции по вводу-выводу.

Важным достоинством выбора МП на основе БПр является то, что она не только определяет время решения задачи на конкретном MП, но и вскрывает достоинства и недостатки его системы команд для заданной области применений. Если проверка правильности составления БПр на конкретных числовых примерах покажет, что БПр не дает удовлетворительных временных показателей ее выполнения, следует использовать один из следующих подходов:

- повторить разработку для этого же МП, но перераспределить при этом программные и аппаратные средства таким образом, чтобы обеспечить требуемые характеристики по быстродействию;

- выбрать более быстродействующий МП.

Процедура выбора МП с помощью БПр приведена на рис. 4.3.

Разработка аппаратной части МПС должна начинаться с разработки ее процессора, поскольку в дальнейшем он может использоваться для проверки других устройств. Обычно в процесс разработки процессора входят этапы по разработке вспомогательного оборудования, которое позволяет упростить проверку и отладку процессора.

В состав МПК БИС в ряде случаев не входит генератор тактовых импульсов, поэтому он должен быть разработан и изготовлен в первую очередь, так как он может быть единственным элементом, необходимым для запуска процессора.

Если МПС реализуется на сравнительно большом числе ИС, а рабочая программа достаточно сложна, то потребуется разработка и изготовление пульта. Он должен иметь индикацию состояния адресной шины и шины данных. Кнопки и переключатели должны обеспечивать управление пуском и остановкой, шаговым режимом и вводом данных и команд в ОЗУ МПС.

Правильность функционирования процессора МПС должна проверяться в режиме выполнения программы. Поскольку платы памяти изготавливаются обычно позже, для проверки процессора необходимо разработать и изготовить макет небольшого ЗУ.

Рис. 4.3. Процедура выбора МП

Проверку рекомендуется начать с выполнения команды условного перехода, которая передает управление самой себе. Это позволит, во-первых, убедиться в работоспособности МП, а, во-вторых, исследовать временную диаграмму работы процессора MПС с помощью осциллографа. На основе макета памяти можно проверить выполнение всех команд, а позже проверить работоспособность остальной аппаратуры МПС.

Характеристики МПС в значительной степени определяются организацией обмена информацией между МП, основной памятью и внешними устройствами. Поэтому разработка интерфейса системы является одним из наиболее ответственных этапов разработки. Сложностъ этого этапа обуславливается тем, что связь БИС, входящих в MПK, обычно функционально и структурно строго регламентирована руководящим техническим материалом, спецификой МПС, предназначенной для конкретного применения, и определяется исключительно внешними устройствами МПС и их связью с МП и основной памятью. На аппаратуру, обеспечивающую этот интерфейс, в некоторых случаях приходится 60-80% общих аппаратурных затрат. В функции интерфейса обычно входят операции по дешифрации адреса устройства, синхронизации обмена, согласование информационных и управляющих сигналов, дешифрация кода команды, генерирование запросов на прерывание процессора и др.