Классификация оперативной памятиРефераты >> Программирование и компьютеры >> Классификация оперативной памяти

2. Direct Rambus Channel создает электрические соединения между Rambus Controller и чипами Direct RIMM. Работа канала основана на 30-ти сигналах, составляющих высокоскоростную шину. Эта шина работает на частоте 400 МГц и, за счет передачи данных на обеих границах тактового сигнала, позволяет передавать данные на 800 МГц. Два канала данных (шириной в байт каждый) позволяет получать пиковую пропускную способность в 1,6 Гбайт/с. Канал соответствует форм-фактору SDRAM.

3. Разъем Direct Rambus —это разъем со 168 контактами. Контакты расположены на двух сторонах модуля, по 84 с каждой стороны. Разъем представляет собой низкоиндуктивный интерфейс между каналом на модуле RIMM и каналом на материнской плате.

4. Модуль RIMM — это модуль памяти, который включает в себя один или более чипов и организует непрерывность канала. По существу, RIMM образует непрерывный канал на пути от одного разъема к другому. Поэтому оставлять свободные разъемы недопустимо

Существуют специальные модули только с каналом, называемые continuity modules. Они не содержат чипов памяти и предназначены для заполнени свободных посадочных мест.

Модули RIMM имеют размеры, сходные с геометрическими размерами SDRAM DIMMs. Модули RIMM поддерживают SPD, которые используются на DIMM'ах SDRAM. В отличие от SDRAM DIMM, Direct Rambus может содержать любое целое число чипов Direct RDRAM (до максимально возможного).

Один канал Direct Rambus максимум может поддерживать 32 чипа DRDRAM. На материнской плате может использоваться до трех RIMM модулей. Используются 64 Мбит, 128 Мбит и 256 Мбит устройства.

Чтобы расширить память сверх 32-х устройств, могут использоваться два чипа повторителя. С одним повторителем канал может поддерживать 64 устройства с 6-ю RIMM модулями, а с двумя —128 устройств на 12 модулях.

5. Чипы DRDRAM. Чипы DRDRAM составляют часть подсистемы Rambus, запоминающие данные. Все устройства в системе электрически расположены в канале между контроллером и терминатором. Устройства Direct Rambus могут только отвечать на запросы контроллера, который делает их шину подчиненной или отвечающей. Устройства включают в себя статическое и динамическое ОЗУ.

4. Оперативная кэш-память.

Как уже отмечалось, для динамической оперативной памяти необходима периодическая ее регенерация. В компьютере это осуществляетс централизовано: организуется цикл прямого чтения/записи содержимого динамического ОЗУ. Эта операция осуществляется с помощью специальной микросхемы. В процессе регенерации микропроцессор переходит в режим ожидания, что снижает производительность системы не менее чем на 5%.

Минимальный цикл обращени микропроцессора к оперативной памяти состоит из двух состояний шины. Подсчитано, что около 70% всех обращений процессора к шине компьютера составляет чтение команд, 20% — чтение и запись данных, и только оставшиеся 10% составляют обращения к устройствам ввода-вывода. Поэтому введение даже одного состояния ожидания при обращении к памяти значительно снижает производительность компьютера. Таким образом, существенный рост быстродействия системы может быть достигнут только при сбалансированной работе подсистемы памяти.

|

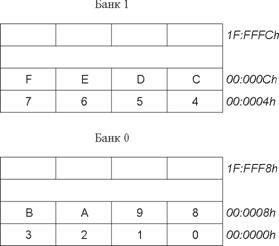

Рис. B.4.1. Система с интерливингом памяти.

В системе с интерливингом —расслоением адресов ячеек памяти —весь объем памяти делится на два или несколько банков. Двойные слова с последовательными адресами располагаются в разных банках. Во время считывания информации из оперативной памяти за один цикл можно организовать параллельное извлечение информации из разных блоков, что уменьшает количество циклов ожидания.

|

Рис. B.4.2. Система со страничной организации памяти.

В системах со страничной организацией памяти вся память делится на фиксированные по размеру зоны адресов —страницы. Обращение к памяти в пределах страницы происходит без ожидания, а при смене страницы —как обычно, с состояниями ожидания.

При страничной организации память делится на строки и столбцы. Адрес обращения к двойному слову содержит 9-ти разрядный номер строки и 9-ти разрядный номер столбца. При обращении к странице сигнал выбора номера строки поддерживается неизменным, а сигнал выбора столбца переставляется на столбец, откуда нужно прочитать данные.

Страничная организация памяти требует для своей реализации особые микросхемы. Они имеют специальный режим – страничный доступ со статической выборкой столбцов (static column decode).

Для полной реализации потенциальных скоростных возможностей микропроцессоров используется многоуровневая иерархическа память. Она включает в себя быстродействующую кэш-память – SRAM. Кэш-память состоит из памяти данных, построенная на микросхемах SRAM, и контроллера кэша. В кэш-памяти хранитс информация, копируемая из основной оперативной памяти. Каждый раз при обращении микропроцессора к памяти контроллер кэш-памяти проверяет наличие данных в кэше. Если эти данные в кэше есть (“попадание”), то микропроцессор получает данные из кэша. Если этих данных нет (“промах”), выполняется обычный цикл обращения к оперативной памяти DRAM.

Основным фактором, определяющим вероятность попадания, является емкость кэш-памяти. Как правило, при объеме кэша в 2 Кбайта вероятность попадания составляет от 50 до 60%. Поскольку размер кэш-памяти на современных компьютерах превышает 256 Кбайт, то вероятность попадания будет выше 90% (дл компьютеров с объемом памяти ~ 16 Мбайт.)

Для реализации кэш-памяти в настоящее время разработаны эффективные однокристальные контроллеры. Наиболее широкое распространени получили контроллеры i82385 фирмы Intel и A38152 фирмы Asustec Microsystems.

Контроллер i82385 поддерживает 32 Кбайта кэш-памяти, и может работать в двух конфигурациях:

13. Кэш-память с прямым отображением.

14. Двухканальная модульно-ассоциативна кэш-память.

|